410 – Miniaturisation et packaging en électronique et en micro-électronique

Pour recevoir les programmes avec tarifs,

faites votre sélection.

€0.00

Taux de satisfaction : 97%

Taux de réussite : 100%

Taux de réussite : 100%

Actualisé en Août 2023

à partir des données de 2022

à partir des données de 2022

Description

PUBLIC CONCERNÉ

Décideurs, responsables d’études, développeurs, chefs de projets, personnel des services R&D et bureaux d’études.

OBJECTIFS

- Connaître les techniques et technologies d’interconnexion et de protection qui existent dans le packaging des composants électroniques.

- Comprendre les mécanismes de défaillance et savoir les anticiper afin de concevoir un assemblage fiable.

PRÉREQUIS

- Savoir lire, écrire et compter, avoir des connaissances en mathématiques et physique.

- Niveau minimum BAC Technique, BAC+2.

- Avoir des connaissances théoriques sur les lignes d’assemblages de produits électroniques.

- Il est recommandé d’avoir assisté aux formations IFTEC N°100 « les cartes électroniques », N°320 « refusion des CMS » et N°310 « brasage à la vague standard et sélective » ou N°100 puis N°300 « brasage des cartes électroniques ».

MOYENS PÉDAGOGIQUES

- Animation par vidéo projection, photos.

- Support PDF imprimable disponible en téléchargement avant la formation.

ÉVALUATION DES ACQUIS

- QCM de 20 questions à livre fermé en début et en fin de stage.

- Le niveau de réussite de la formation est conditionné à un score minimum : obtention de la moyenne lors du QCM final.

PROGRAMME

1 – PRÉAMBULE

- Le Packaging d’une fonction, qu’est-ce ?

– Pourquoi le packaging ?

– Niveaux d’application

– Packaging traditionnel

– Les nouvelles attentes - Grandes options d’intégration

– Substrats et MCM

– Boîtiers et Encapsulation plastique

– La miniaturisation - Évolution de l’électronique, et du Packaging

– Composants enterrés

– les procédés FanOut / In

2 – MATÉRIAUX, NOTIONS DE BASE

- Les Multicouches céramiques

- Les Polymères, qu’est-ce ?

- Les thermoplastiques et thermodurcissables

- Les MMC, qu’est-ce ?

3 – NÉCESSITÉ DE PROTÉGER LE COMPOSANT ÉLECTRONIQUE

- Qu’est-ce que le composant électronique, structure ?

– Notion de composant actif nu

– Notion de composant actif encapsulé

– Le collage des puces nues

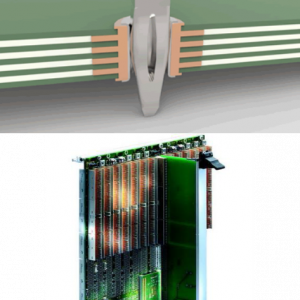

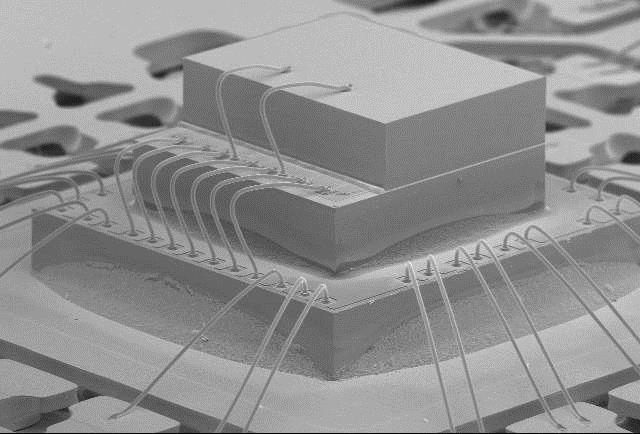

– Le câblage filaire - Les risques encourus.

– Mécanismes de défaillance des composants actifs

– Origines des problèmes

4 – MATÉRIAUX EN ÉLECTRONIQUE

- Applications en électronique

- Matériaux pour substrats, conducteurs, diélectriques, boîtiers

- Les Polymères en électronique

- Matériaux de Hautes performances

5 – HERMÉTICITÉ–HUMIDITÉ

- Notion d’herméticité et calculs associés

- Limites admissibles et raison

- Pseudo-Herméticité des Composants plastiques

- Humidité Stockage, Manipulation, Préparation

6 – ÉVACUATION DE LA CHALEUR

- Le boîtier, élément de dissipation

- Solutions, Techniques de refroidissement

- Éléments de calculs thermiques

– La conduction

– La convection

– Le rayonnement - Table de valeurs ( CTH et CTE )

7 – DISTRIBUTION DE LA PUISSANCE ET DES SIGNAUX, LE SUBSTRAT

- Rôles et types du Substrat d’interconnexion

– Place dans l’architecture packaging

– Familles technologiques - Alimentations et électronique rapide

– Relations performances / packaging

– Notions de bruit

– Capacité de découplage intégrée - Distribution dense des signaux

– Problèmes de couplages électromagnétiques et capacitifs

– Solutions topologiques

8 – LES TECHNIQUES MULTI CHIP MODULES

- Techniques de stratification – Substrats

– Rappels, couches minces ou épaisses

– Architecture MCM – Grandes familles : MCM-S, MCM-D, MCM-C et MCM-L

– Évolution et Variantes - Techniques dérivées

– Couches épaisses haute densité

– SBU et Microvias : Perçage, Stratification, Finition et Test - Techniques d’assemblage et problèmes connexes

– Assemblage des Puces nues

– Rendement et problèmes de réparation

– Performances et Limitations actuelles - Techniques d’approvisionnement des puces nues

– Principes généraux du KGD

– Wafer-Level Burn-in

9 – LES BOÎTIERS EN ÉLECTRONIQUE

- Boîtiers hermétiques

– Familles disponibles

– Boîtiers verre-métal

– Boîtiers céramiques - Encapsulation plastique

– Principe ; Réalisation ; Matériaux

– Familles de composants

– Risques pour le composant - Assemblage : cas particulier du BGA

– Difficultés en conception

– Brasage des BGA

– Réparations, rebillage des composants

– Incidence des défauts sous les BGA, rendement

10 – AUTRES TYPES DE PACKAGING

- FLIP CHIP et Underfill, TAB, COB et variantes

- Package on Package (PoP), QFN, PQFN

- Wafer Level Package (WLP), Fan-Out (chip first, chip last approaches)

- Through Silicon/Polymer Via (TSV/TPV)

- 3D Interconnexion

CONCLUSION – DISCUSSION

- Évolutions proches

- Évolutions futures

Informations complémentaires

| DURÉE DU STAGE | 26 heures en 4 jours |

|---|---|

| SANCTION | Attestation de stage non soumise au score obtenu à l’issue du QCM final. Le score obtenu par le participant sera indiqué sur l’attestation. |

| NOMBRE DE STAGIAIRES | Maximum par session = 8 |

| FORMATEUR | – M. Alexandre VAL, consultant |

| SESSION 2024 | À Bourg la Reine : |

| ACCESSIBILITÉ AUX PERSONNES EN SITUATION DE HANDICAP | Oui |